Thin Shrink Small Outline Package (TSSOP)

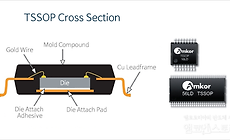

Thin Shrink Small Outline Package (TSSOP) ‘더 작게, 더 많은 입출력, 더 빠르게, 더 가볍게’라는 기치 아래 탄생한 앰코의 TSSOP는 SOP의 리드 피치를 줄이는 것뿐만 아니라 0.9mm에 이르는 얇은 두께의 패키지 생산을 가능하게 했습니다. 앰코는 부단한 연구를 통하여 진보된 설계, 어셈블리 장비/프로세스/재료에서도 품질과 신뢰성을 확보하였습니다. 결과적으로, 패키지의 편평도(flatness)를 유지하고 와이어 스윕(wire sweep), 솔더 부착성(solderability), 딜레미네이션(delimination)을 해결할 수 있었습니다. 앰코는 IC 디자이너, 패키지 엔지니어, 회로 설계자, 부품 전문가들과 긴밀한 공조를 통해 TSSOP 생산라인에서 성공적인 성..

2015. 11. 13.

Thin Shrink Small Outline Package (TSSOP)

Thin Shrink Small Outline Package (TSSOP) ‘더 작게, 더 많은 입출력, 더 빠르게, 더 가볍게’라는 기치 아래 탄생한 앰코의 TSSOP는 SOP의 리드 피치를 줄이는 것뿐만 아니라 0.9mm에 이르는 얇은 두께의 패키지 생산을 가능하게 했습니다. 앰코는 부단한 연구를 통하여 진보된 설계, 어셈블리 장비/프로세스/재료에서도 품질과 신뢰성을 확보하였습니다. 결과적으로, 패키지의 편평도(flatness)를 유지하고 와이어 스윕(wire sweep), 솔더 부착성(solderability), 딜레미네이션(delimination)을 해결할 수 있었습니다. 앰코는 IC 디자이너, 패키지 엔지니어, 회로 설계자, 부품 전문가들과 긴밀한 공조를 통해 TSSOP 생산라인에서 성공적인 성..

2015. 11. 13.