반도체 패키징 기술의 변천사

The History of Packaging Technologies

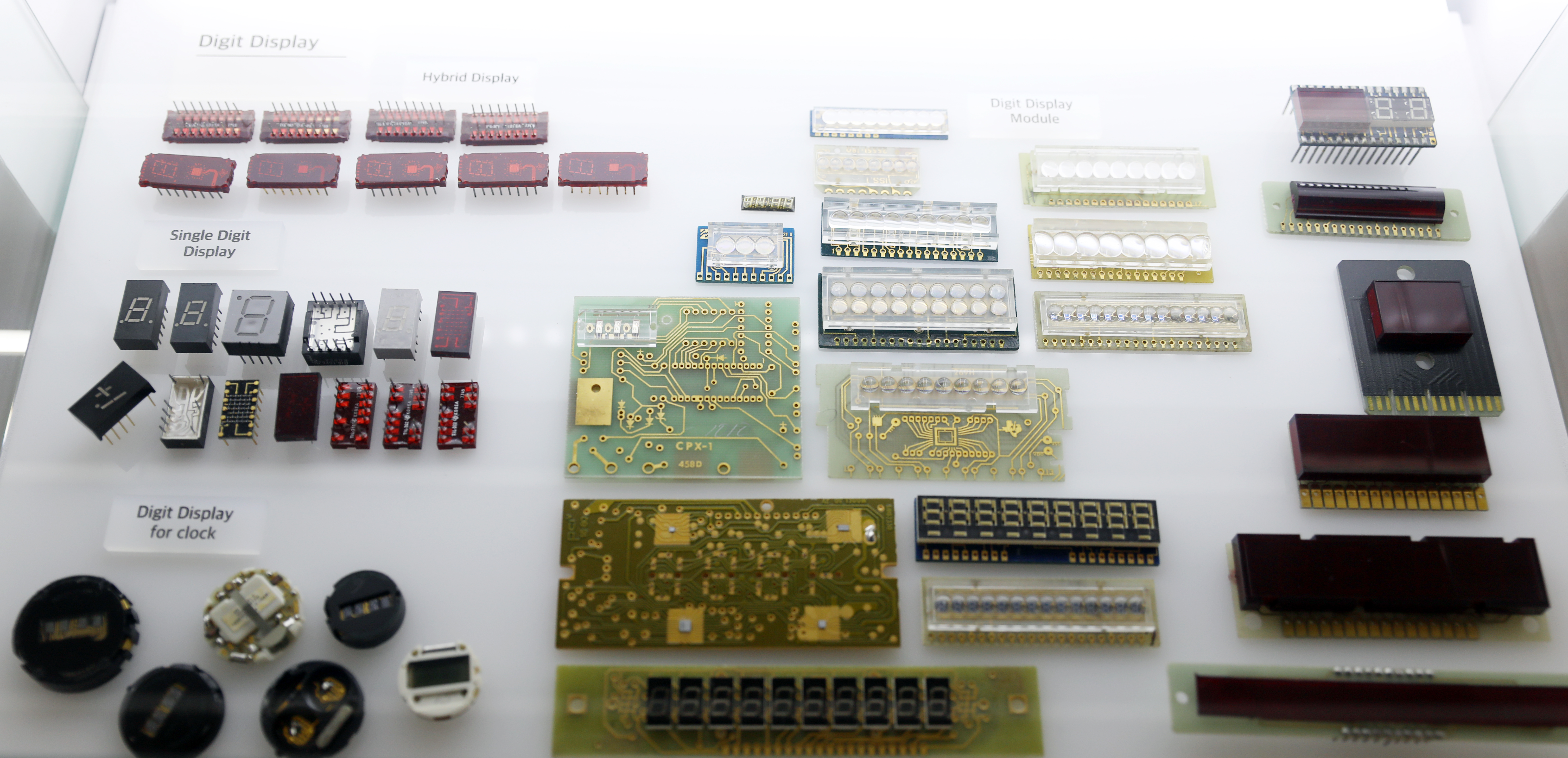

1950~1970's

Metal Can Package

조그마한 원형 회로기판 바닥에 2-10개의 핀이 있고 회로기판 위에 칩을 올린 다음, 원통형 금속을 씌운 패키지.

Dual In-line Package (DIP)

증가하는 핀 수를 수용하기 위해 직사각형의 기다란 두 측면에 핀을 나오게 하는 패키지.

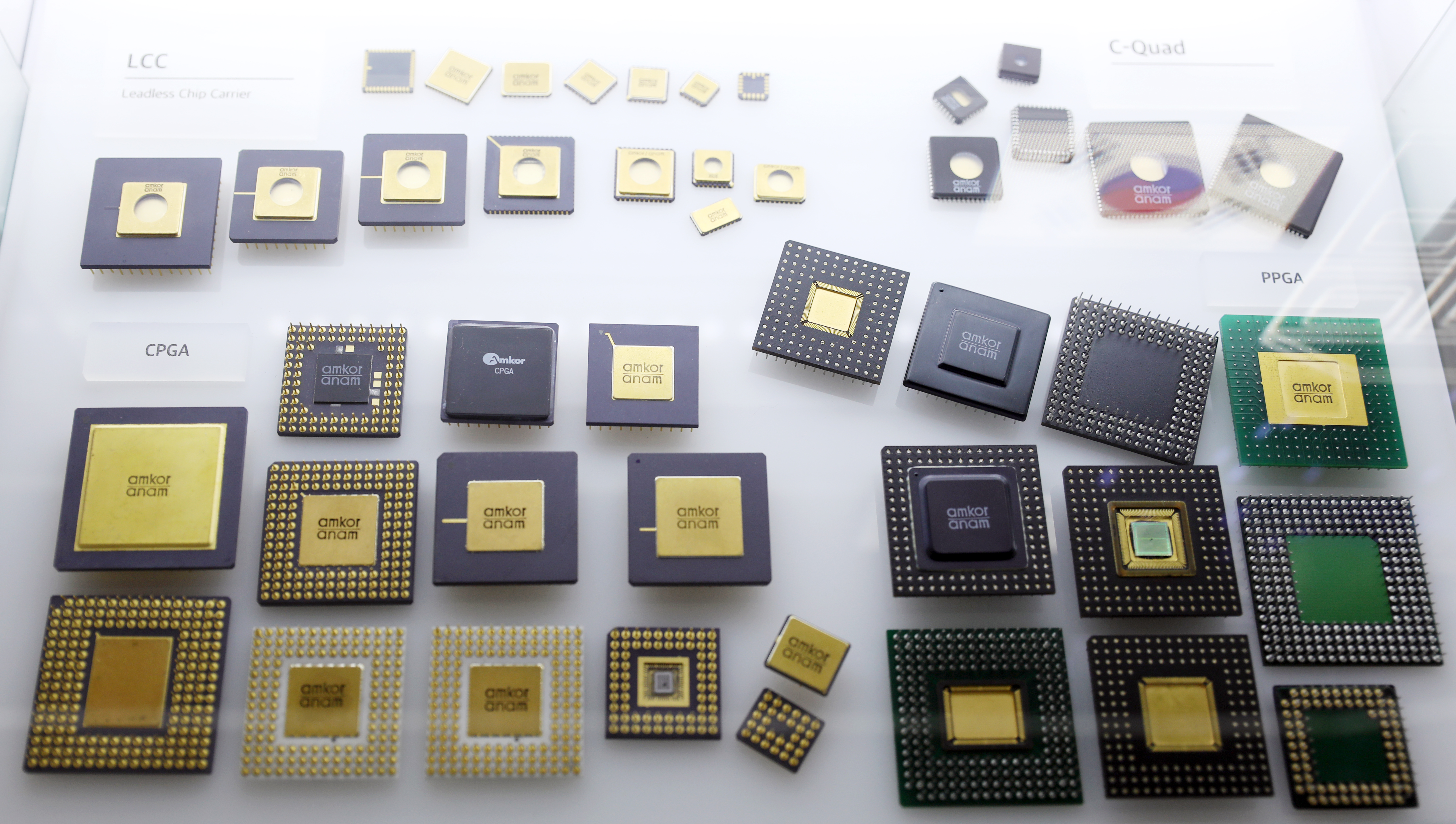

Pin Grid Array (PGA)

IC가 점차 복잡해지면서 패키지의 바닥면 전체에 핀을 배열하고 Through Hole 방식이나 소켓에 삽입하는 방식으로 보드에 실장하는 패키지.

1980's

Small Outline Integrated Circuit (SOIC)

이전에 개발된 DIP 등이 부품실장을 할 때 보드 구멍에 리드를 꽂는 Through Hole 방식을 사용하였다면, SOIC는 표면실장기술(Surface Mount Technology)을 사용하고 DIP와 비교해 실장면적이 30~50% 가량 작은 패키지.

Chip Carrier Package (CCP)

표면실장을 사용하고 크기는 DIP보다 작으며, 패키지의 4면을 모두 사용하기 때문에 핀 개수는 더 많은 패키지.

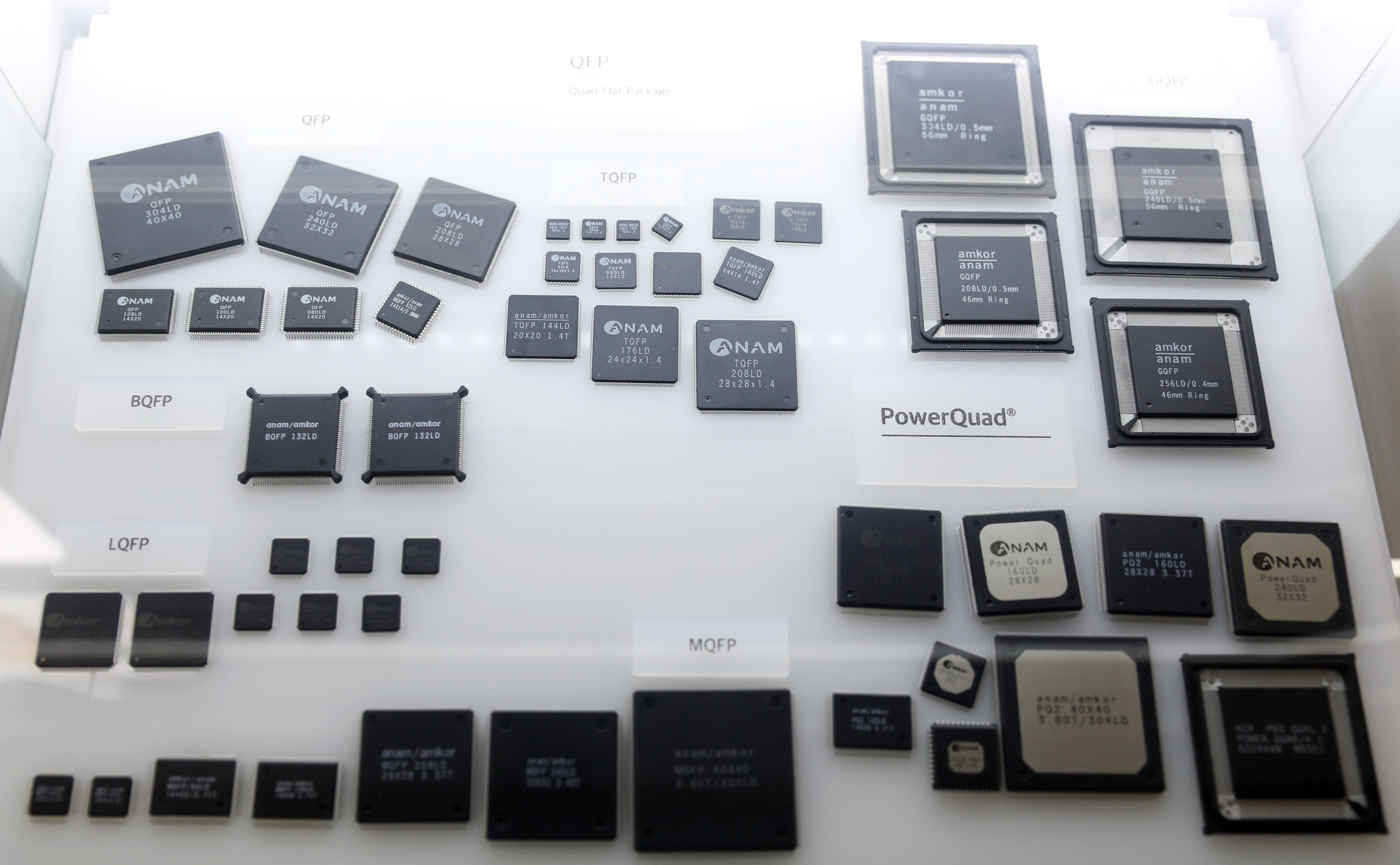

Quad Flat Package (QFP)

표면실장을 사용하고, 정사각형 또는 직사각형 모양이며, 4면에 모두 리드가 있는 패키지. 패키지 크기와 리드 피치, 리드 수에 따라 LQFP (Low Profile QFP), TQFP (Thin QFP) 등으로 구분.

1990's

Thin Packages

기존 패키지의 두께를 0.9~1.0mm로 현격히 줄인 패키지로 TSOP, TQFP, TSSOP 등이 있다.

Ball Grid Array (BGA)

PGA와 유사한 구조이지만, 기판이 세라믹에서 플라스틱으로 바뀌고 긴 다리 모양의 핀이 솔더볼로 교체되며 최대 수용 핀 수가 획기적으로 증가함. 이 BGA를 전환점으로 하여 패키지 기술은 비약적인 도약을 하게 되었다.

MicroLeadFrame® (MLF®)

앰코의 MLF® 패키지는 전자제품의 소형화, 경량화에 따라 패키지 크기를 줄이고, 리드 부분이 바닥에 평면으로 닿도록 하여 물리적 신뢰도를 향상하였다.

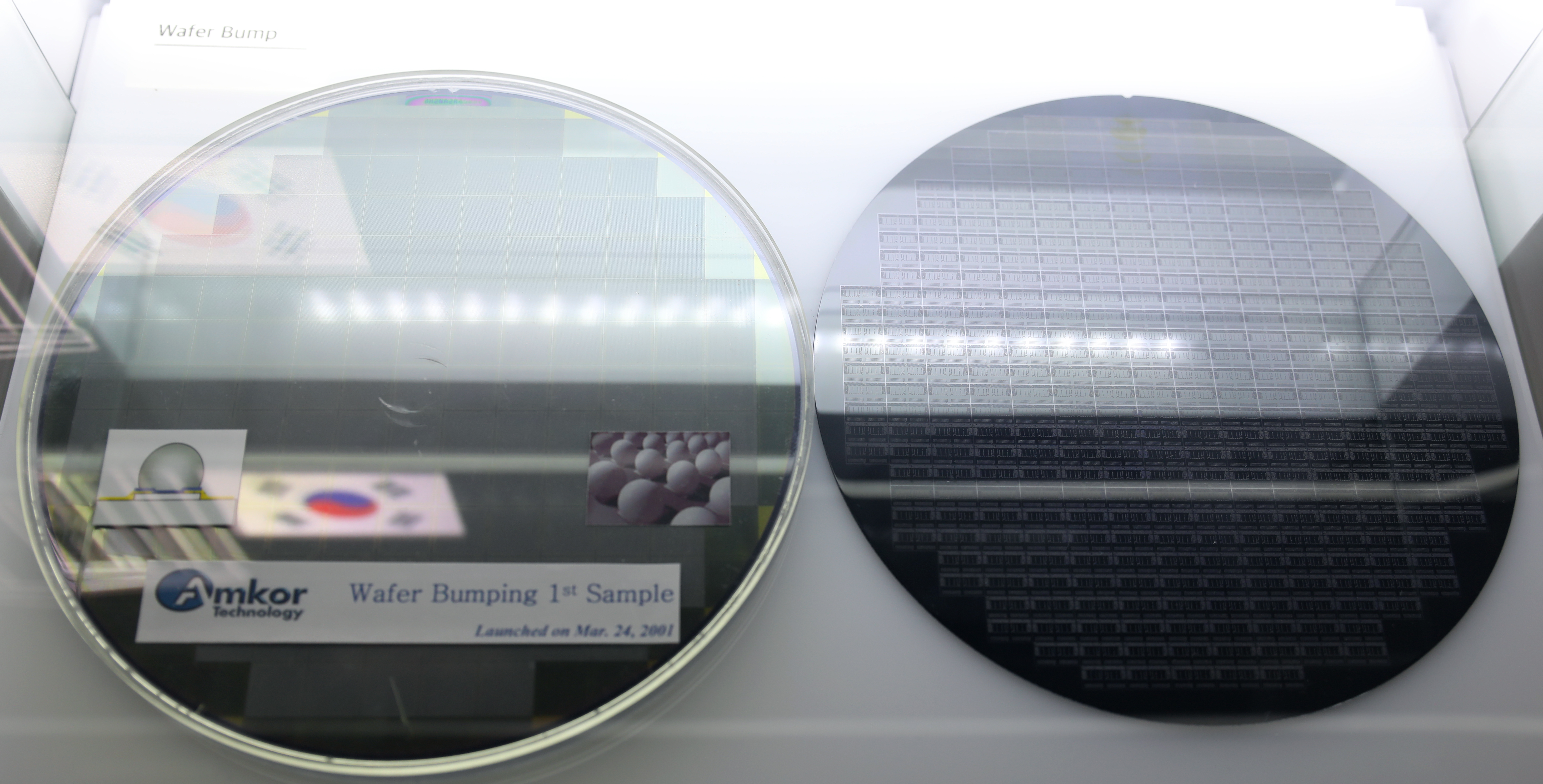

2000’s

Chip Scale Package (CSP)

패키지의 크기가 칩 크기와 거의 동일한 패키지로, 두께가 매우 얇고 WLCSP와 같이 웨이퍼상에서 곧바로 패키징을 완료하기도 한다.

Wafer Bumping

반도체 칩과 기판을 연결하는 와이어 본딩을 대체한 기술로, 이 범프가 형성된 칩을 뒤집어서 기판에 장착시키면 플립칩 패키지가 된다.

3D Package

하나의 패키지에 여러 개의 칩을 적층(Stack)하거나, 와이어 본딩을 대체하는 플립칩(Flip Chip) 기술을 적용하는 패키지. 또는 기능이 다른 여러 칩을 하나의 패키지 기판 위에 올려놓고, 칩과 칩을 와이어 본딩이나 플립칩 같은 기술을 이용하여 연결한 다음 하나의 패키지로 완성하는 SiP (System in Package) 등 3차원 입체 패키징.

앰코코리아 메타버스 홍보관 바로가기